What is the difference between 3D Packaging, 25D interposers, and 3D ICs?Current Developments in 3D Packaging With Focus on Embedded Substrate Technologies March 15 1 Embedding in PCBs & Inorganic Substrates 2 High Temp DieAttach & HighLead Solder 3 Thermal Management 4 Packaging Technologies 5 Interposers 6 Embedded Resistors 7 5G Packaging Die attach equipment Advanced packaging industry Overview SysteminPackage (SiP) Automotive packaging Advanced substrates Wafer Level Packaging (WLP) Equipment & materials for 3DIC & WaferLevel Packaging applications

System In Package Thrives In The Shadows

2.5 d vs 3d packaging

2.5 d vs 3d packaging- Full 3D vs 25D Processing Elizabeth 1758 This option is designed for modeling of structures and care must be taken to collect proper overlap This option is not designed for use over large areas or areas with lots of trees3D packaging software for designers, tradeshops & converters Simply put, Studio will help you to produce better artwork Whether you are a designer trying out different ideas, or a prepress operator checking a backmatch, with Studio you are virtually holding the pack in your hands

Http Ewh Ieee Org Soc Cpmt Presentations Cpmt1404a Pdf

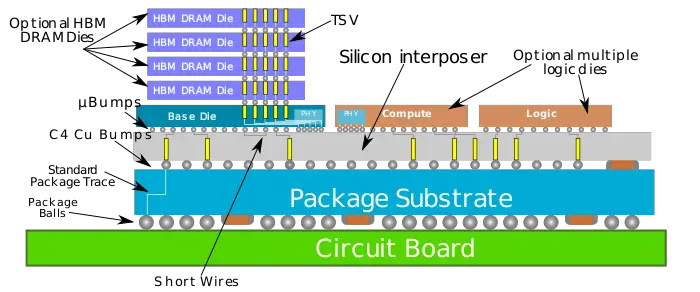

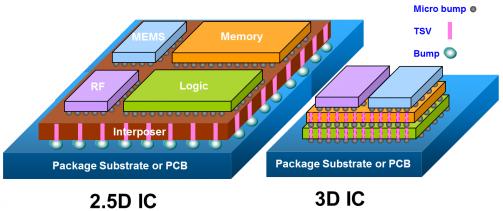

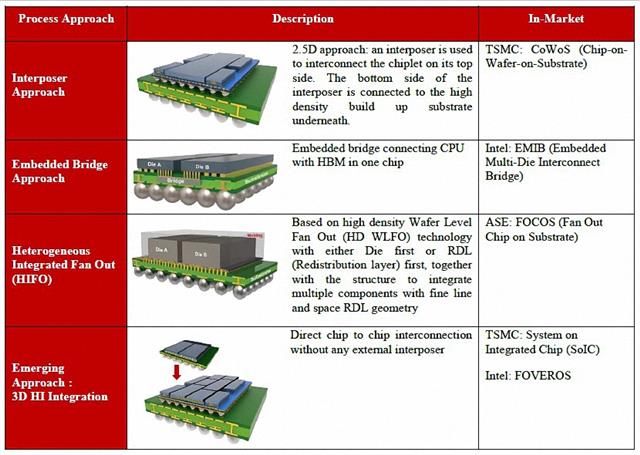

3D TSV in market is estimated to grow at the highest CAGR during the forecast period The major factors driving the 3D IC and 25D IC market for 3D TSV include highest interconnect density and greater space efficiencies in 3D TSV compared to all other types of advanced packaging, such as 3D WLCSP and 25 D• 25/3D packaging process and materials are more sophisticated than in the traditional flip chip packaging technology o The industry mainstream SoA 25/3D package assembly process, materials, and business model are not currently compatible with low volume production for mil/space components • 3D TSV and 25 packaging platforms are gaining interests for highperformance applications

3D printing is one of the latest trends across the packaging industry Although the process is timely and costly, with the time it may drive consumer demand to a great level 3D printing is one of the latest trends across the packaging industry Although the process is timely and costly, with the time it may drive consumer demand to a great levelThe material presented will also reference 3D packaging standards and recognize innovative technologies from a number of industry sources, roadmaps and market forecasts Key words 25D, 3D Semiconductor Package Technology, Through Silicon Via, TSV, Through Glass Via, TGVThe material presented will also reference 3D packaging standards and recognize innovative technologies from a number of industry sources, roadmaps and market forecasts Key words 25D, 3D Semiconductor Package Technology, Through Silicon Via, TSV, Through Glass Via, TGV

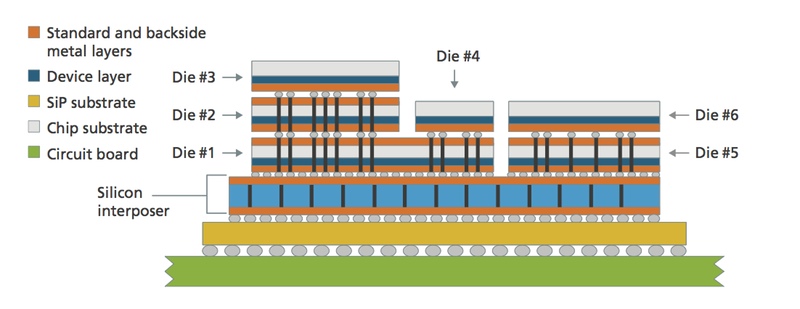

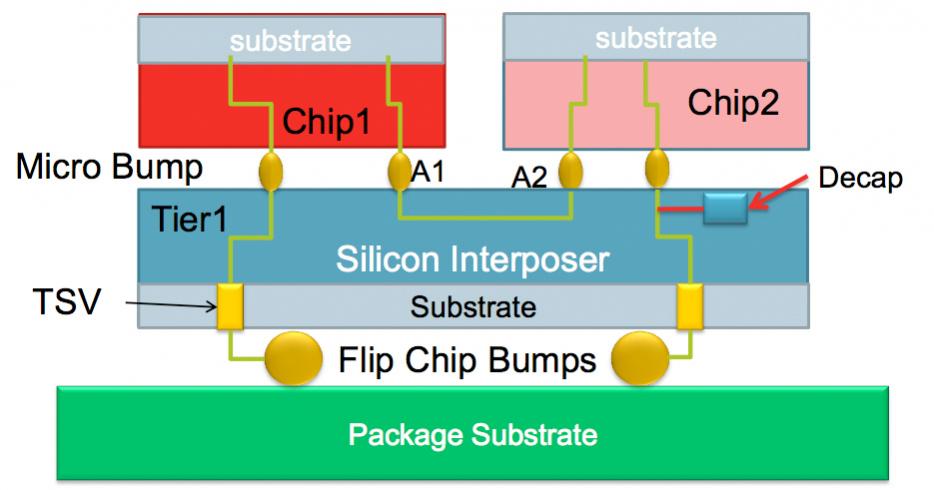

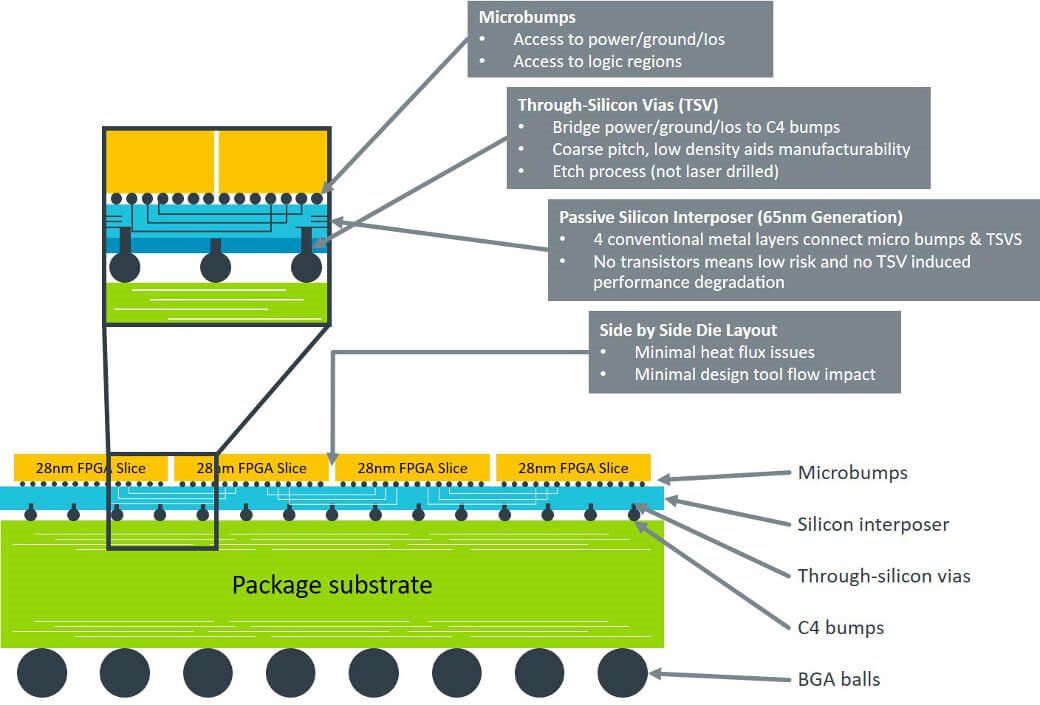

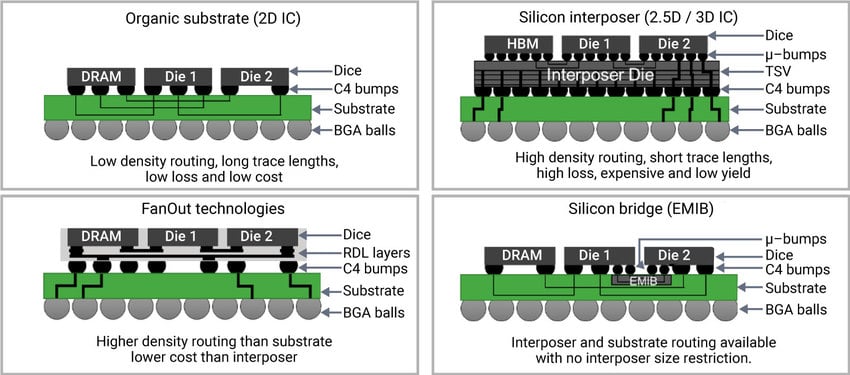

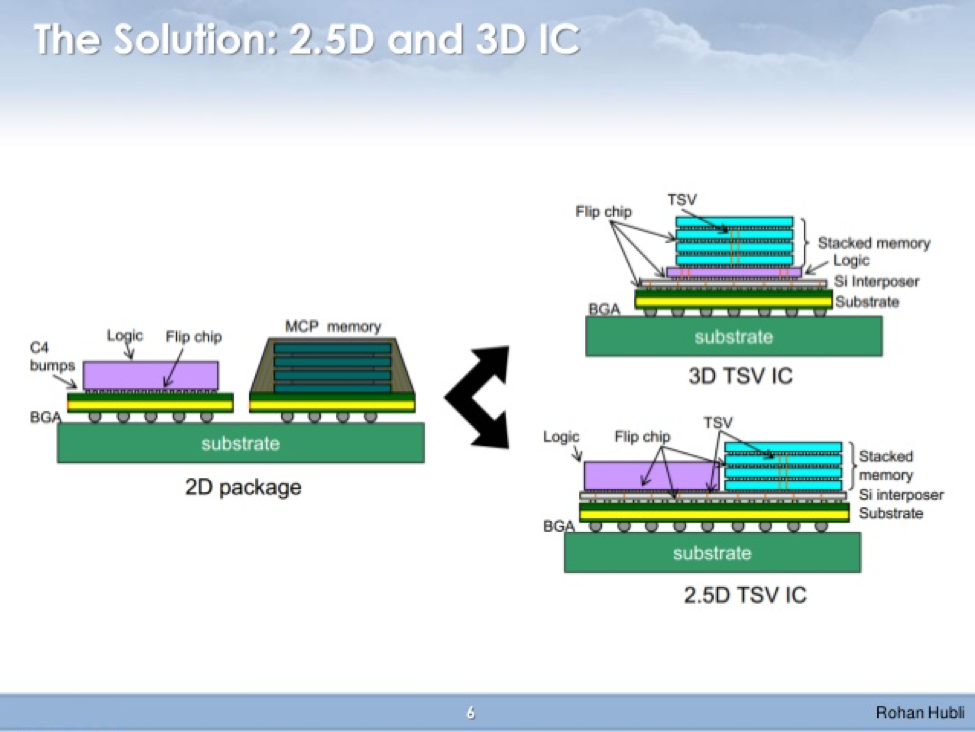

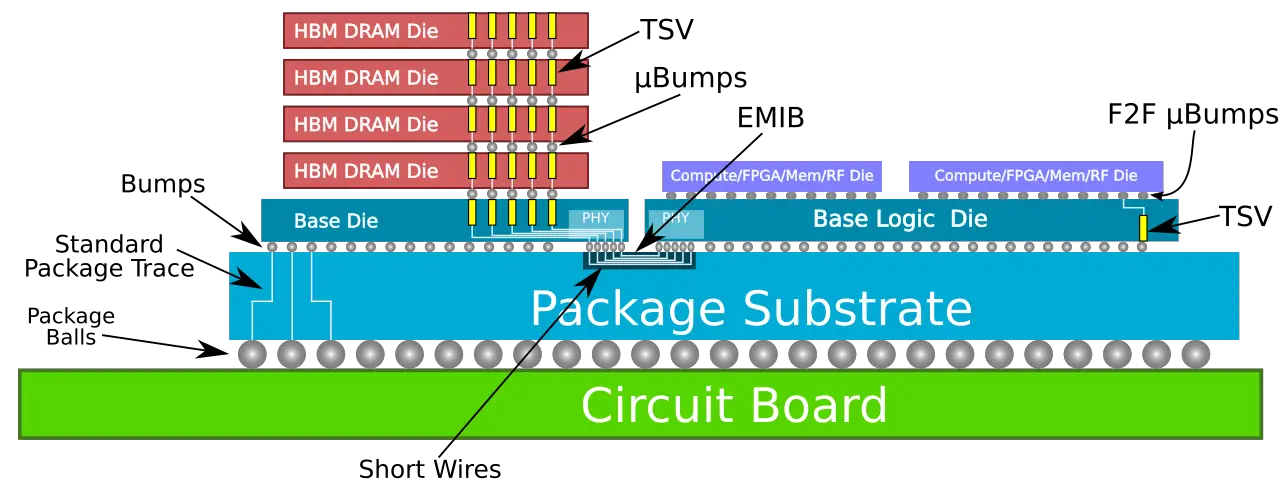

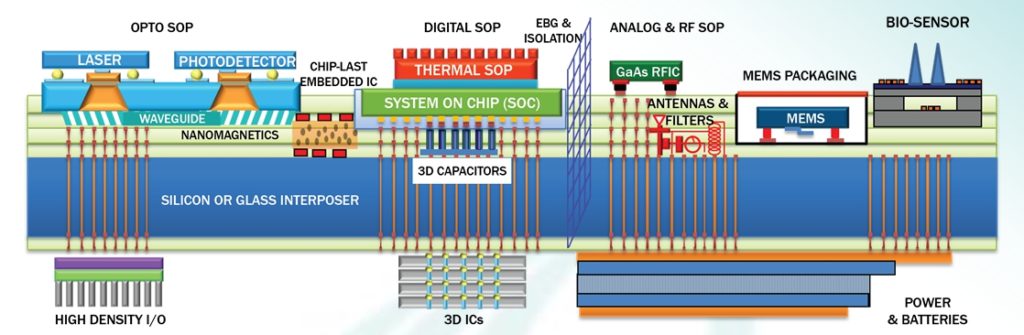

A 25D integrated circuit (25D IC) combines multiple integrated circuit dies in a single package without stacking them into a threedimensional integrated circuit (3DIC) with throughsilicon vias (TSVs) The term "25D" originated when 3DICs with 25/3D IC Packaging Technologies Part 1 Overview IEEE/CPMT, Herb Reiter eda2asic Consulting IncHerb Reiter, eda2asic Consulting, Inc herb@eda2asiccom 1 eda2asic AGENDA Part 1 Introduction eda2asic EndUseMarkets for 25/3D25D/3D TSV & Wafer Level Integration Technology & Market updates 19 Sample wwwyolefr ©19 13 In this report ADVANCED PACKAGING PLATFORMS Focus on 3D stacking packaging platforms in this report No substrate FanOut WLCSP Organic substrates Wirebond BGA CSP COB BOC WB CSP LGA FlipChip BGA FC BGA FO on Substrate 25/21D 3D* CSP LGA

2 5d 3d Packaging Applications Indium Corporation

A Schematics Of The Three Integration Approaches 2d 3d And 2 5d Download Scientific Diagram

While 3D printing has been around for many years, industrial use of 3D printers in India, Singapore and other countries for packaging has just started to get traction 3D printing of packaging provides many advantages over conventional packaging methods Much of this is because of improvements in 3D printing technologyAdvantages of 3D/25D chips Challenges in making 3D chips using Through Silicon Via (TSV)Stanford University's class on nanomanufacturing, led by Aneesh NaiUse the model to for your product Include supplier specific details and incoming die preparation in your analysis View the detailed costs—including labor, material, capital, tooling, and

2 5d Chiplet Integration With An Interposer Download Scientific Diagram

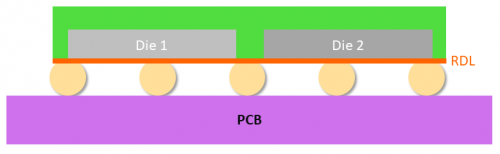

Fan Out Chip On Substrate Ase Group

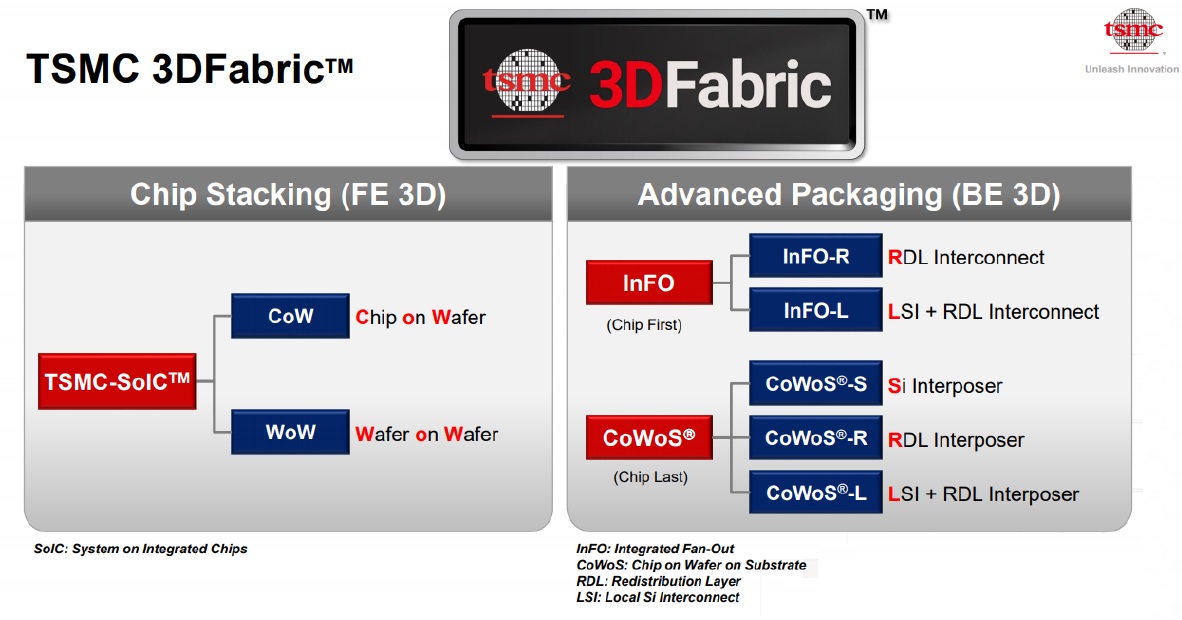

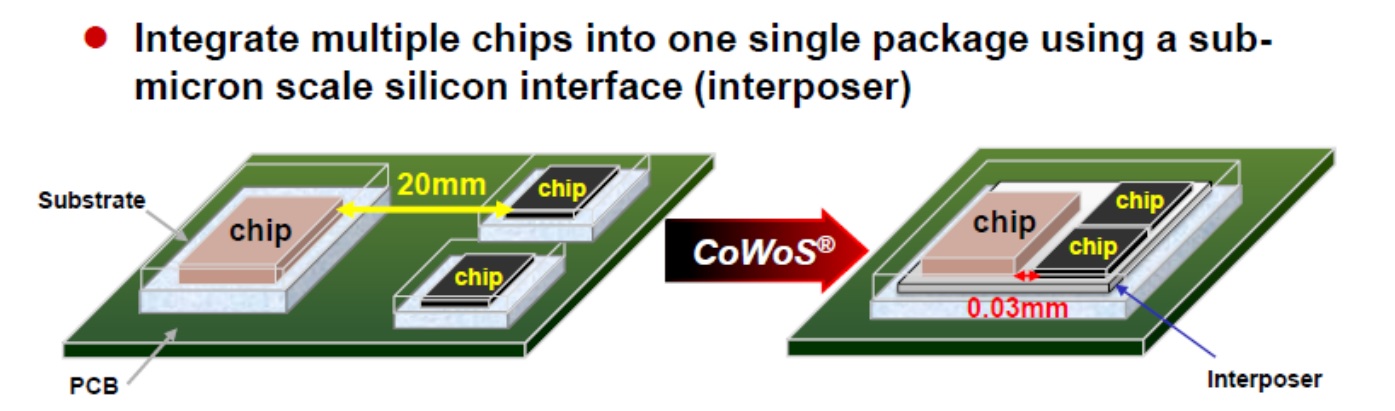

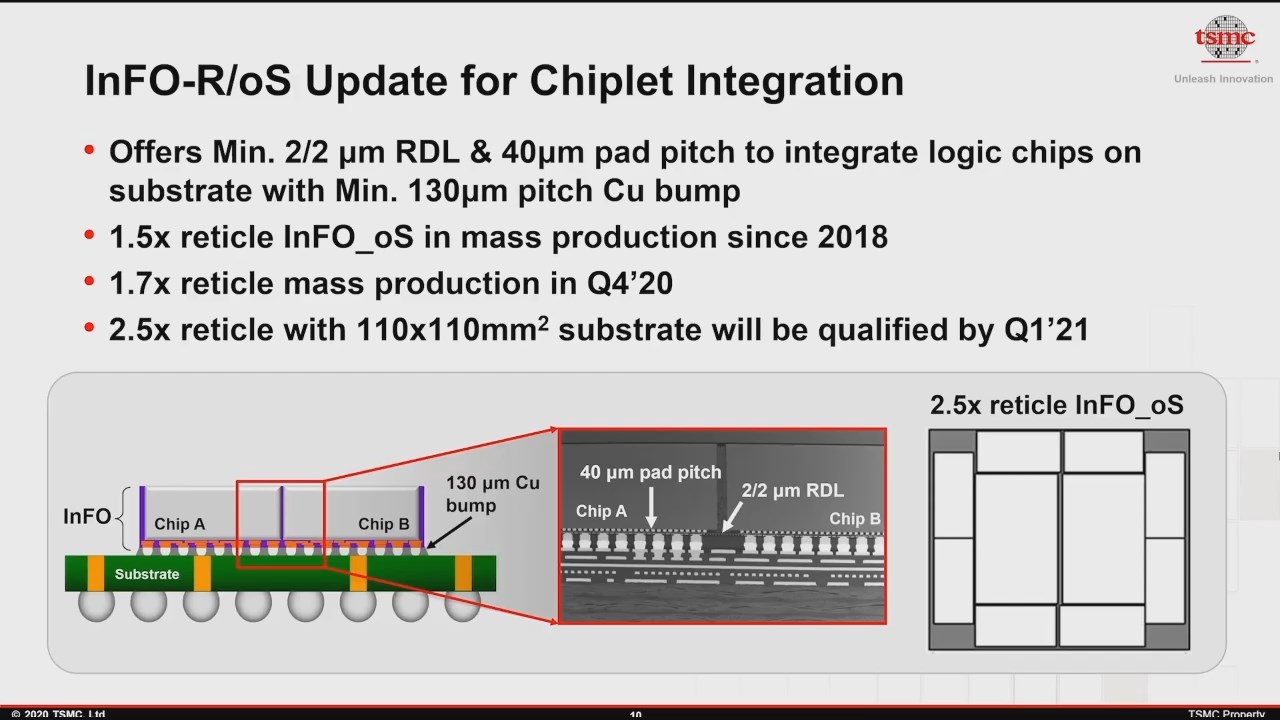

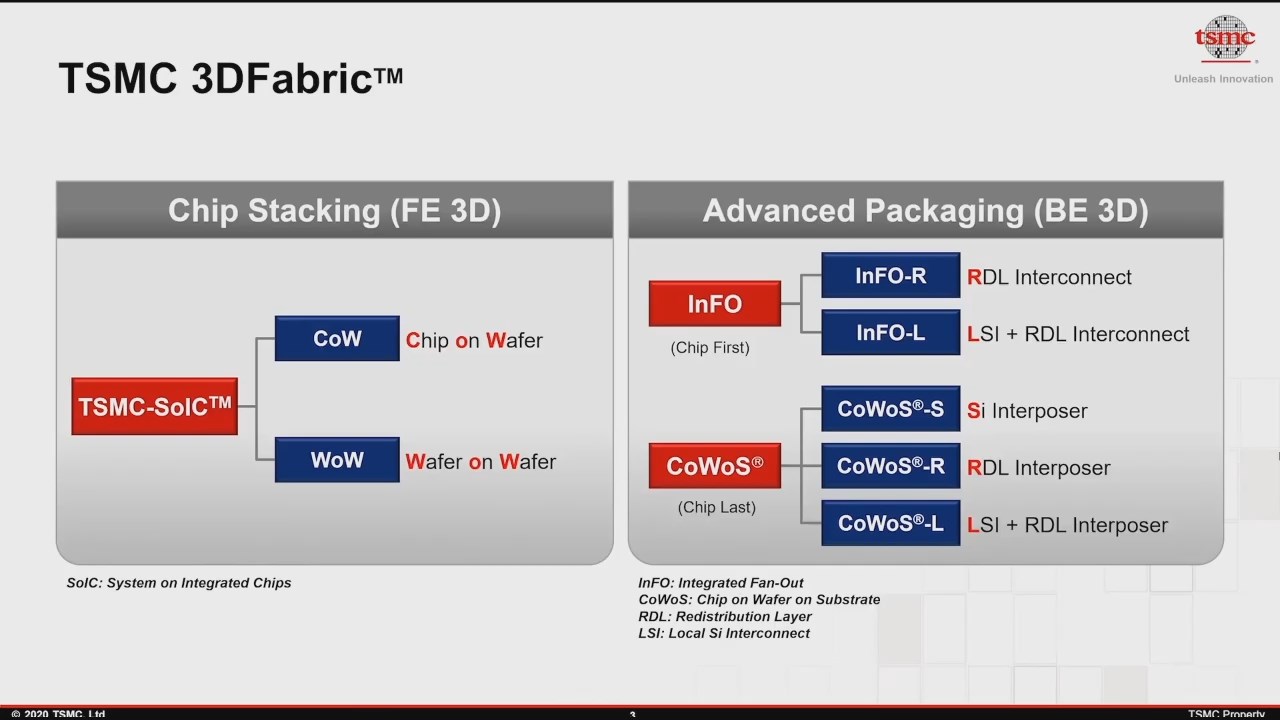

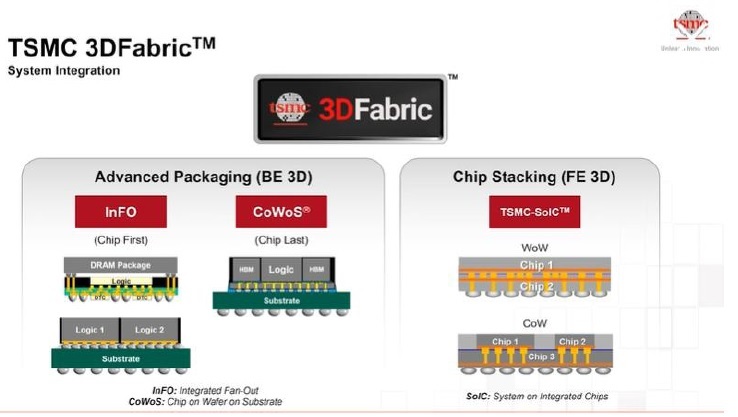

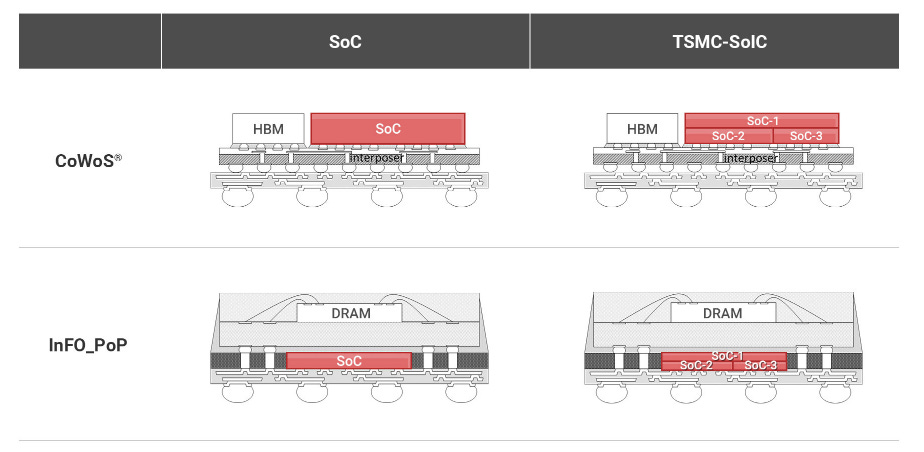

Dug out my #3dprinted #fingerprint stool while doing some packing This is one of my largest ever 3D prints, taking almost 5 days and 14Kg of PLA on a @bigrep3dprinters ONE The design blends between 2 different fingerprints on both sides and took about 30hrs to In order to unify all the different names it gives to its variants of its 25D and 3D packaging, TSMC has introduced its new overriding brand 3DFabric 3DFabric makes sense as a brand to tie theASE is one of the pioneers in 25D/3D packaging technology and has successfully introduced the mass production of the world's first 25D IC package equipped with High Bandwidth Memory (HBM) 25D refers to die stacking package using interposers to achieve the best performance of internet connectivity An Si interposer with TSV (Through Silicon

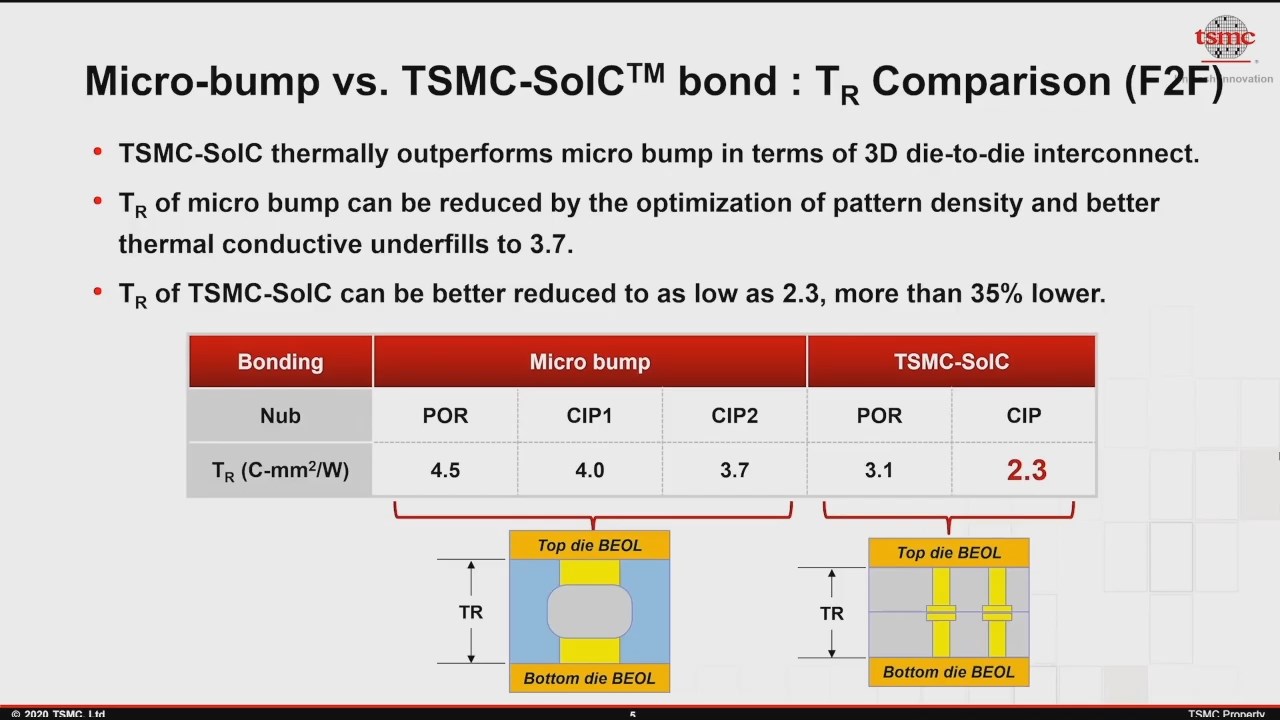

Highlights Of The Tsmc Technology Symposium Part 2 Semiwiki

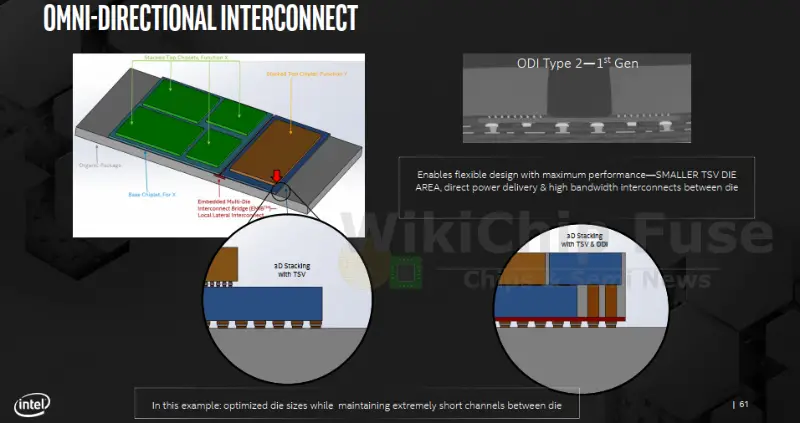

Left Right Above And Under Intel 3d Packaging Tech Gains Omnidirectionality Wikichip Fuse

How to create your 3D packaging design If you want an amazing 3D packaging that stands out from the competition, work with a professional designer Find and hire a designer to make your vision come to life, or host a design contest and get ideas from designers around the world 3D Printing for Medical Packaging—Shifting the Design Cycle Universal Protective Packaging, Inc (UPPI), an industry leader in thermoformed protective packaging, has embraced 3D printing in product developmentCreating packaging for medical products poses special challenges—an elevated need for sterility, repeatability and durability—and UPPI uses 3D printing to prove out packagingLike 3D ICs, 25D assemblies save power by using shorter connections Depending on the design of the onboard devices, they may also avoid using ESD (electrostatic discharge) protection between the devices ESD protection has a large power budget, so the assembly may consume a great deal less power than an equivalent circuit board

Typical Structure Of 2 5d Ic Package Utilizing Interposer Not To Scale Download Scientific Diagram

Typical Structure Of 2 5d Ic Package Utilizing Interposer Not To Scale Download Scientific Diagram

25D & 3D Packaging Cost Model Which applications are right for this technology? The Market Needs a New Kind of 3D Field Solver As shown in the figure below, the 25D and 3D parasitic extraction tools market currently consists of Finite element method (FEM)/boundary element method (BEM) tools (3D), which use numerical solvers to Difference Between Packing and Packaging • Packing and packaging are closely related concepts though being totally different • Packing refers to wrapping up of a single item into a casing so that it arrives in the market in a beautiful manner such as toothpaste and crèmes arriving in their packets • Packaging is mostly done by factory

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Intel Leans Hard On Advanced Chip Packaging Technologies In Battle For Computing Supremacy Venturebeat

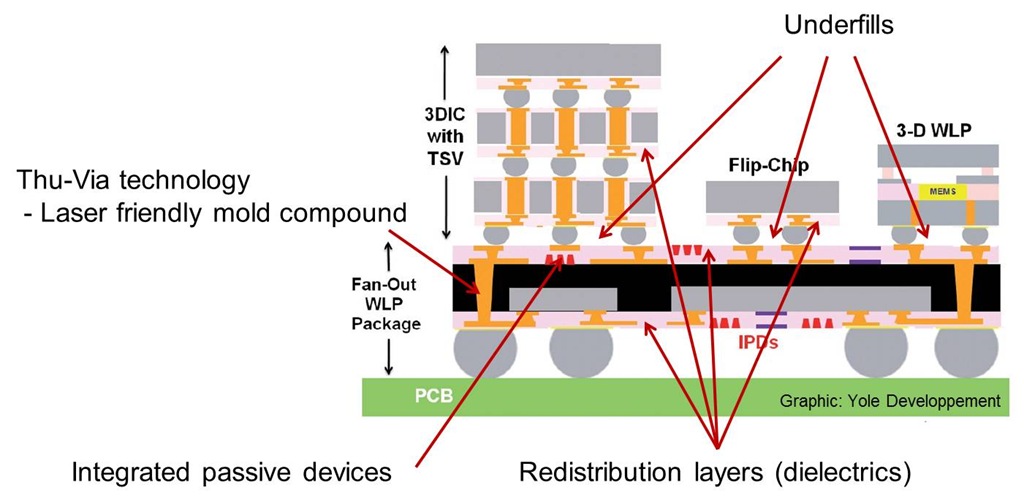

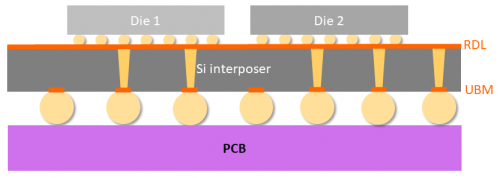

3D Packaging May 09 Applied Materials, Inc Physical Vapor Deposition (PVD) is the preferred approach for depositing UBM and RDL layers, based on the maturity, flexibility, and low cost of the PVD process An appropriate selection of metals combined with optimized wafer treatment and deposition processes directly affects the reliability of The overall IC packaging market is projected to reach $68 billion in 19, up 35% over 18, according to Yole Développement Of those figures, advanced packaging is projected to grow at 43% in 19, compared to 28% for traditional/commodity packaging, according to Yole More 25D/3D and chiplets IC packaging is important for several reasons3D packaging models for download, files in 3ds, max, c4d, maya, blend, obj, fbx with low poly, animated, rigged, game, and VR options

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Chip On Wafer On Substrate Cowos Tsmc Wikichip

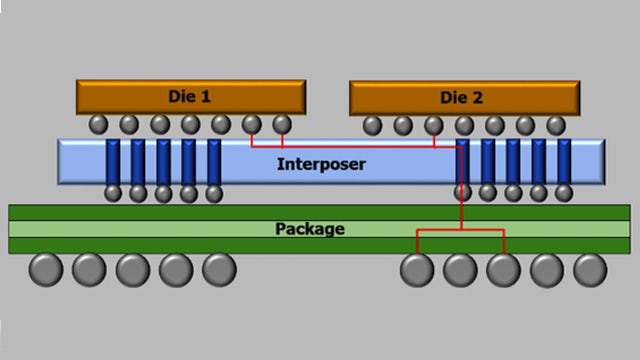

25D is a packaging methodology for including multiple die inside the same package The approach typically has been used for applications where performance and low power are critical Communication between chips is accomplished using either a silicon or organic interposer, typically a chip or layer with throughsilicon vias for communication 除了先進製程之外,先進封裝也成為延續摩爾定律的關鍵技術,像是 25D、3D 和 Chiplets 等技術在近年來成為半導體產業的熱門議題。究竟,先進封裝是如何在延續摩爾定律上扮演關鍵角色?而 25D、3D 和 Chiplets 等封裝技術又有何特點? 人工智慧(AI)、車聯網、5G25/3D HI Packaging – Foundation and Future Vision Author Douglas J Sheldon Subject 21 NEPPETW Presentation Created Date AM

3d Ic And 2 5d Ic Packaging Market In Depth Analysis Taiwan

System In Package Ase Group

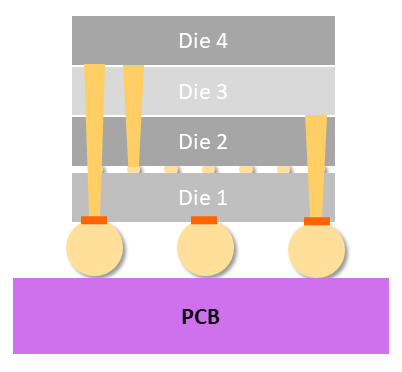

1325D/3D TSV & Wafer Level Integration Technology & Market updates 19 Sample wwwyolefr ©19 In this report ADVANCED PACKAGING PLATFORMS Focus on 3D stacking packaging platforms in this report No substrate FanOut WLCSP Organic substrates Wirebond BGA CSP COB BOC WB CSP LGA FlipChip BGA FC BGA FO on Substrate 25/21D 3D* CSP LGASee how Studio helps you design packaging in 3D Work on oneup files, on multipart packaging and on POP displaysTry it for free https//wwweskocom/en/pro3D packaging refers to 3D integration schemes that rely on traditional methods of interconnect at the package level such as wire bonding and flip chip to achieve vertical stacks

Polymer Challenges In Electronic Packaging Overview Polymer Innovation Blog

Packaging Wars Begin

Chip Packaging Part 4 25D and 3D Packaging Dr Navid Asadi's group examines 25D and 3D packaging for expanding capabilities and capacities of chip solutions Peter Xi 3D IC and 25D IC Packaging Market Report study provides in detail information to understand the imperative market parts that aligns with the business decision related to raw materials, demand, and production capacity The analysis provides demands for the future, besides the opportunities that are available for individual Most CAM programs support 25D milling Vectric Cut 2D and V Carve do a great job 3D milling refers to the CNC's ability to move X, Y and Z all at the same time in a synchronized fashion to create contoured bottoms, sides and tops of objects Many times this will be called 3D carving of material

Eight Requirements For Successful 3d Ic Design

Insights From Leading Edge Just Another Solid State Technology Sites Site Page 21

3D printing filaments are chosen to closely match the target materials Step 1 CAD design A new packaging design is created in CAD software Step 2 Selection of target materials Target materials are chosen to achieve the packaging looks and purpose Step 3 Selection of filaments The tight packing of the hexagon is denoted as HCP In one repeated unit, this arrangement has two layers of spheres The main distinction between hexagonal close packing and cubic close packing is that there are 6 spheres in a unit cell of hexagonal close packing, whereas there are 4 spheres in a unit cell of cubic close packing 523 3D Ic Packaging Technology 524 2D Vs 25D Vs 3D Ic Packaging Technology 53 System in Package (SIP) – By Packaging Type 531 Ball Grid Array 625 Others 63 Communications Sector

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Beyond Apple M1 Achieving Maximum Density And Flexibility Through 3d Stacking Coreteks

Through Silicon Via (TSV) interconnects have emerged to serve a wide range of 25D TSV and 3D TSV packaging applications and architectures that demand very high performance and functionality at the lowest energy/performance metric To enable the use of TSVs in 25D/3D TSV architectures, we have developed several backend technology platforms to 2D vs 25D vs 3D ICs 101 By Max Maxfield 6 I see a lot of articles bouncing around the Internet these days about 25D and 3D ICs One really good one that came out recently was 25D ICs are more than a stepping stone to 3D ICs by Mike Santarini of Xilinx On the other hand, there are a lot of other articles that have "3D ICsJanuary of 07, we declared "Packaging Saves the World!" and in January of 08, the cover story was " Packaging Drives the Industry" Of course this was when the only 3D stacking technology was Package on Package (PoP) 3D ICs were still a gleam in researchers' eyes, and the term 25D hadn't even been coined yet

Semiconductor Packaging 3d Ic Emerging As Innovation Enabler Semiwiki

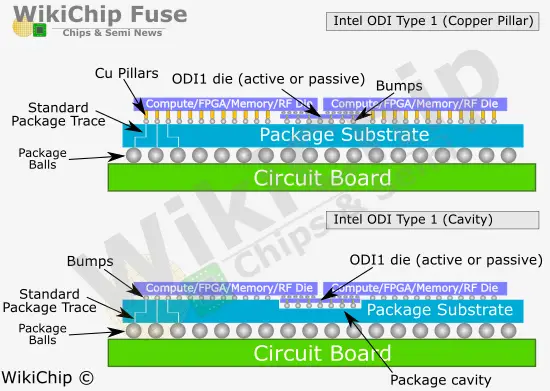

Left Right Above And Under Intel 3d Packaging Tech Gains Omnidirectionality Wikichip Fuse

25D & 3D Packaging Indium Corporation is a world leader in the design, formulation, manufacture and supply of semiconductorgrade fluxes and associated materials, enabling 25 and 3D assembly processes, as well as more standard flipchip assembly Stencil technology has evolved throughout the years, and SysteminPackage solder pastes requireFree 3D packaging models for download, files in 3ds, max, c4d, maya, blend, obj, fbx with low poly, animated, rigged, game, and VR optionsDetails Dosch 3D Packaging Design V2 contains 150 hires 3Dmodels for packaging and product design The 3Dmodels are each fully textured, and all that needs to be done for a finished product design is to put the product label on the 3Dobjects, or maybe to change colors The product saves substantial time with the presentation of many

Iftle 381 Tsmc Wow Insights From Leading Edge

2 5d

Eps Ieee Org Images Files Hir 19 Hir Ch22 2d 3d Pdf

Lost In The Advanced Ic Packaging Labyrinth Know These 10 Basic Terms Edn

Imec Arm Demonstrate Backside Power Delivery

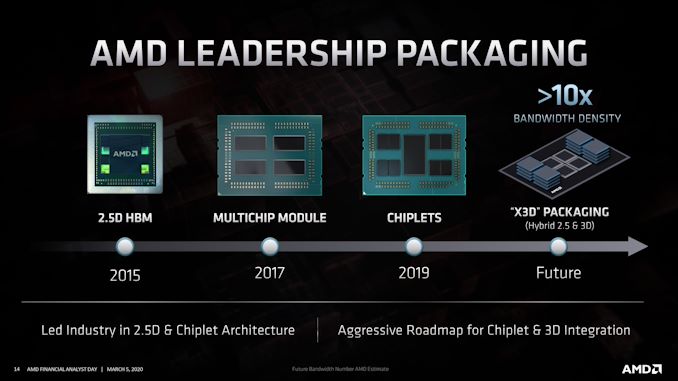

Amd Discusses X3d Die Stacking And Packaging For Future Products Hybrid 2 5d And 3d

Www Semiconductors Org Wp Content Uploads 18 06 2 15 Itrs 2 0 Herogeneous Integration Pdf

2 5d And 3d Designs Semiwiki

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Nepp Nasa Gov Workshops Etw18 Talks 19june18 1330a sheldon nepp etw djs final Pdf

Advanced Packaging Five Trends To Watch In 17 Electronic Products

Three Dimensions In 3dic Part I Research Articles Arm Research Arm Community

Http Www Cetimes Com Sip 18 Download 1 Sp 2 Pdf

Figure 1 From 2 5d 3d Tsv Processes Development And Assembly Packaging Technology Semantic Scholar

Iftle 468 Samsung Advanced Packaging At The Virtual Iwlpc 3d Incites

Http Ewh Ieee Org Soc Cpmt Presentations Cpmt1404a Pdf

About 2 5d Technology Nhanced Semiconductors Inc

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

3d 2 5d Ic Based Obfuscation Springerlink

Http Ewh Ieee Org Soc Cpmt Presentations Cpmt1105a Pdf

3d Packaging Breaking New Ground Yole Pradeep S Techpoints

2 5d Fo Wlp Issues Come Into Focus

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Www Xilinx Com Publications About 3 D Architectures Pdf

3d And 2 5d Packaging Assembly With Highly Silica Filled One Step Chip Attach Materials For Both Thermal Compression Bonding And Mass Reflow Processes Semantic Scholar

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Production Test Of System In Package With Die To Die Phy Ip

Design Electrical Mechanical Thermal Prc Gatech Edu Georgia Institute Of Technology Atlanta Ga

Www Circuitinsight Com Pdf 2 5d 3d Semiconductor Package Technology Ipc Pdf

Interposer Wikipedia

Insights From Leading Edge Insights From Leading Edge Page 4

Www Nist Gov Document Bottomspdf

2 5d And 3d Ics New Paradigms In Asic Product Engineering Blog Einfochips

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Advanced Semiconductor Packaging Starting To Change Memory Market Landscape Seeking Alpha

1

Semiconductor Packaging Inspection Teraview

System In Package Thrives In The Shadows

Advanced Packaging Strong Momentum Driven By Tsmc Intel And Samsung Ee Times Asia

3d Ic And 2 5 D Ic Packaging Industries In Depth Analysis

2 5d Semiconductor Engineering

Conventional Process Flow For 2 5d 3d Ic Integration Chip On Download Scientific Diagram

Overcoming Advanced Soc Routing Congestion With 2 5d System In Packaging Embedded Com

17 European 3d Summit Making Advanced Packaging Great Again

Fan Out Wafer Level Packaging The Samtec Blog

Design Guideline On Board Level Thermomechanical Reliability Of 2 5d Package Sciencedirect

Eetimes 3d Ic Design

Plasma Etch And Deposition Solutions For 2 5d 3d Packaging Spts

Intel Looks To Advanced 3d Packaging For More Than Moore To Supplement 10 And 7 Nanometer Nodes Wikichip Fuse

2 5d Ics Or Interposer Technology Youtube

Highlights Of The Tsmc Technology Symposium 21 Packaging Semiwiki

About 2 5d Technology Nhanced Semiconductors Inc

Yole Yole Developpement Yole Developpement Yole Development System Plus System Plus Consulting Piezoelectric Bulk Bulk To Thin Film Thin Film Piezo Sensors Actuators Transducers Mobile And Consumer Automotive And Transportation Defense

Pin On Telecharger Gratuit

Semicap Primer Packaging History And Primer By Mule Mule S Musings

Integrated Circuit Packaging And Gct The Samtec Blog

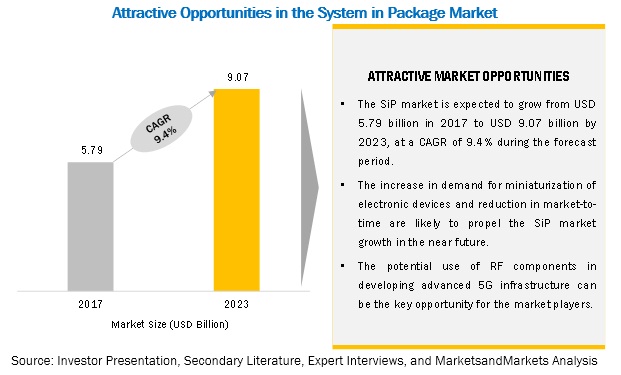

System In Package Market By Packaging Technology Package Packaging Method Device Application Covid 19 Impact Analysis Marketsandmarkets

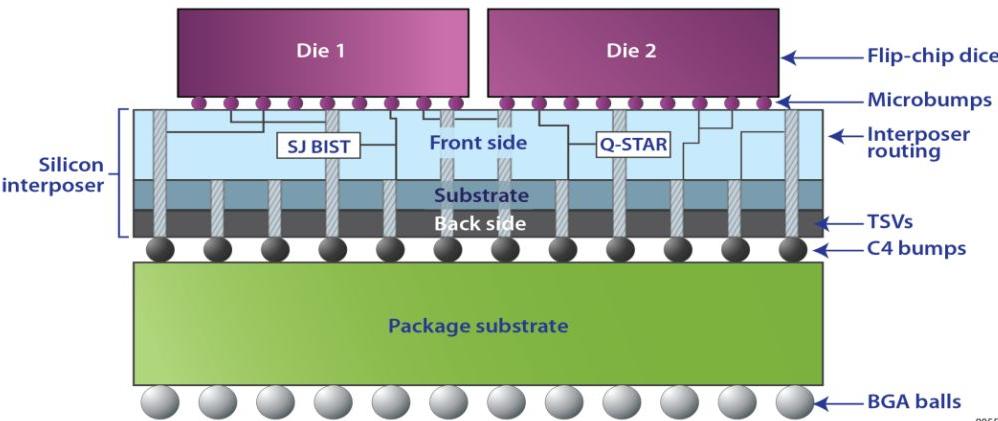

Tsv Bist Die Level Integrity Monitors Ridgetop Group

What S The Best Advanced Packaging Option Cyberoptics

2 5d 3d Ase Group

More 2 5d 3d Fan Out Packages Ahead

Plasma Etch And Deposition Solutions For 2 5d 3d Packaging Spts

Semiconductor Foundry Support Siemens Digital Industries Software

1

Intel Looks To Advanced 3d Packaging For More Than Moore To Supplement 10 And 7 Nanometer Nodes Page 2 Wikichip Fuse

Plasma Etch And Deposition Solutions For 2 5d 3d Packaging Spts

Choose Through Silicon Via Tsv Packaging For Improved Performance Anysilicon

Advanced Packaging Five Trends To Watch In 17 Electronic Products

Sorting Out Packaging Options

3d And 2 5d Packaging Assembly With Highly Silica Filled One Step Chip Attach Materials For Both Thermal Compression Bonding And Mass Reflow Processes Semantic Scholar

/article-new/2015/11/tsmc_chip_packaging-800x400.jpg?lossy)

Patent Applications Reveal Apple S Research Into 3d Chip Packaging Macrumors

Three Dimensional Integrated Circuit Wikipedia

Automated Latch Up Verification In 2 5d 3d Ics In Compliance Magazine

Iftle 464 Tsmc S Family Of Packaging Technologies Are Built On 3d Fabric 3d Incites

Increased Funds Could Catalyze Tsmc S 3d Ic Research News

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

3d Multi Chip Integration And Packaging Technology For Nand Flash Memories Springerlink

2 5d And 3d Ics New Paradigms In Asic Product Engineering Blog Einfochips

1

C44f5d406df450f4a66b 1b94a87dd9446df0a9ca62e142 Ssl Cf2 Rackcdn Com 18 12 Amkor 2 5d Package And Hdfo Technical Article En Pdf

The Evolution Of Heterogeneous Integration Enables The Coming Ai Era

0 件のコメント:

コメントを投稿